こんにちは。今日は、DVFSの元となった、動的電圧スケーリング(DVS)開発の背景をお伝えします。

動的電圧スケーリング(DVS)とは?

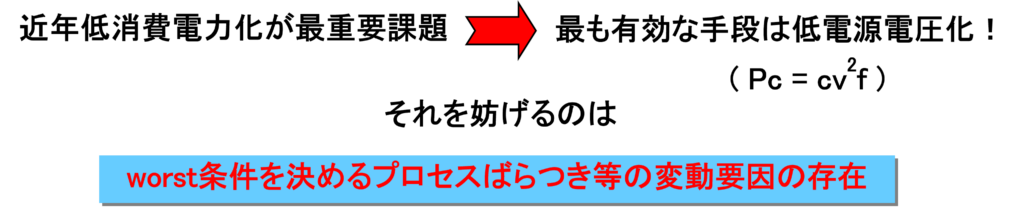

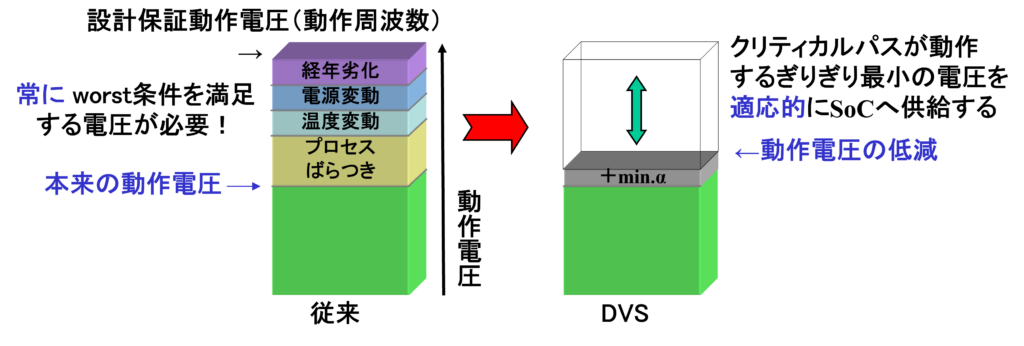

近年マーケットからLSIの低消費電力化が強く求められていく時代でありながら、従来SoCのSPECで規定されていた設計補償動作電圧では、本来欲しい動作電圧に比べて大きなマージンを含んだ電圧が必要となり、それが低消費電力化の障害となっていました。

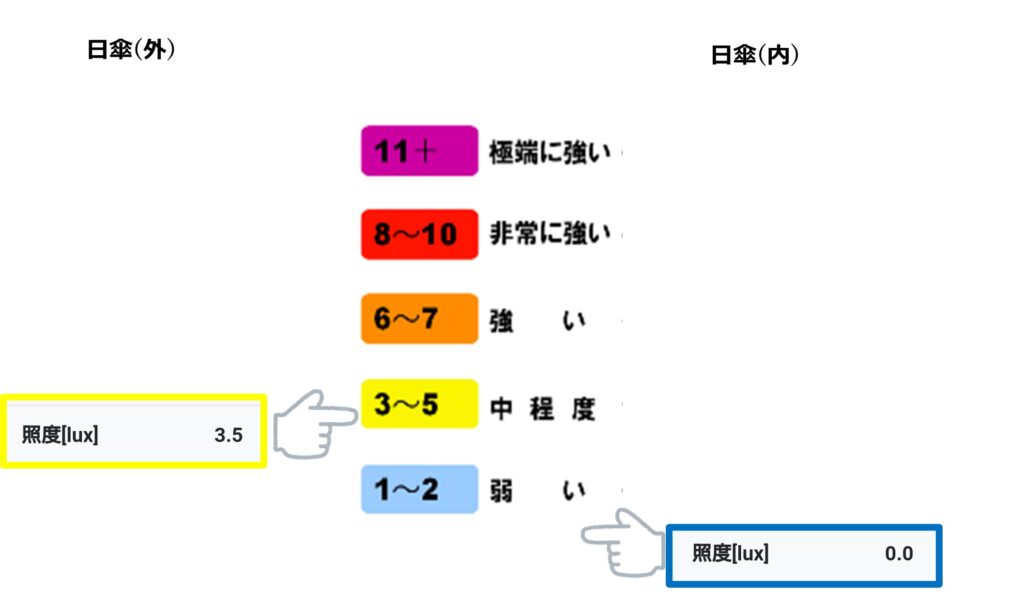

そこでDVSが登場したのです。一言で言うと、DVSは、SoC内のクリティカルパスが動作するぎりぎり最小の電源電圧Vddを適応的にSoCに供給する技術です。どういうことか分かりやすくするため、動的電圧スケーリング(DVS)開発の背景を図示しました。

左側が従来の設計補償動作電圧、右側がDVSです。SoCにおけるプロセスばらつき、温度変動、電源電圧変動、経年劣化等のworst条件を満足させるため、本来必要な動作電圧に比べ無駄に大きかった動作保証電圧の閾値を、右のDVSではクリティカルパスが動作するギリギリ+αの最小電圧をアダプティブにSoCに供給するため、動作電圧を低減し省電力化に貢献できます。

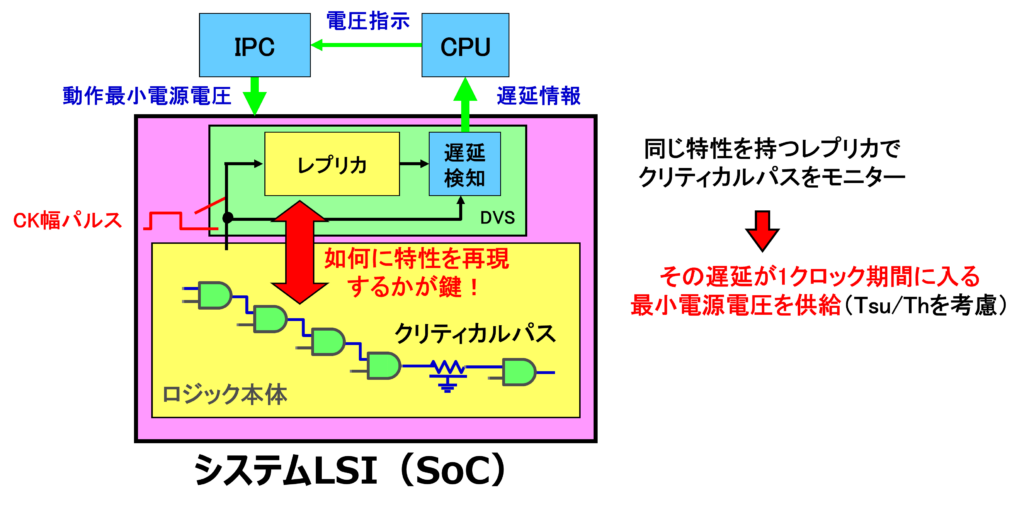

レプリカによるクリティカルパス監視がDVS技術の肝

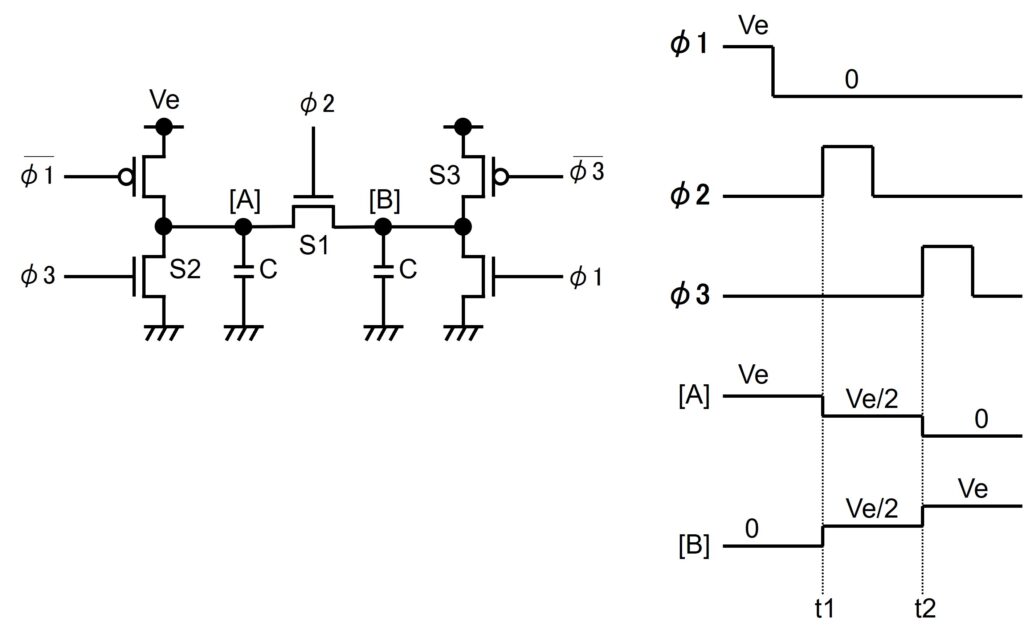

図2にプロセスばらつき/温度変動等に対応したDVSを紹介します。SoC内部のクリティカルパスと同等の遅延時間を有するレプリカ回路を用意し、レプリカの遅延時間がクロック1周期内に入るギリギリ最小の電源電圧をSoCに供給します。

無論電源電圧供給ではTsu/Thを考慮しますが、こうしたレプリカによるクリティカルパスモニターが、設計マージンの最小化を可能した結果、低消費電力化が実現しています。

DVSの効果

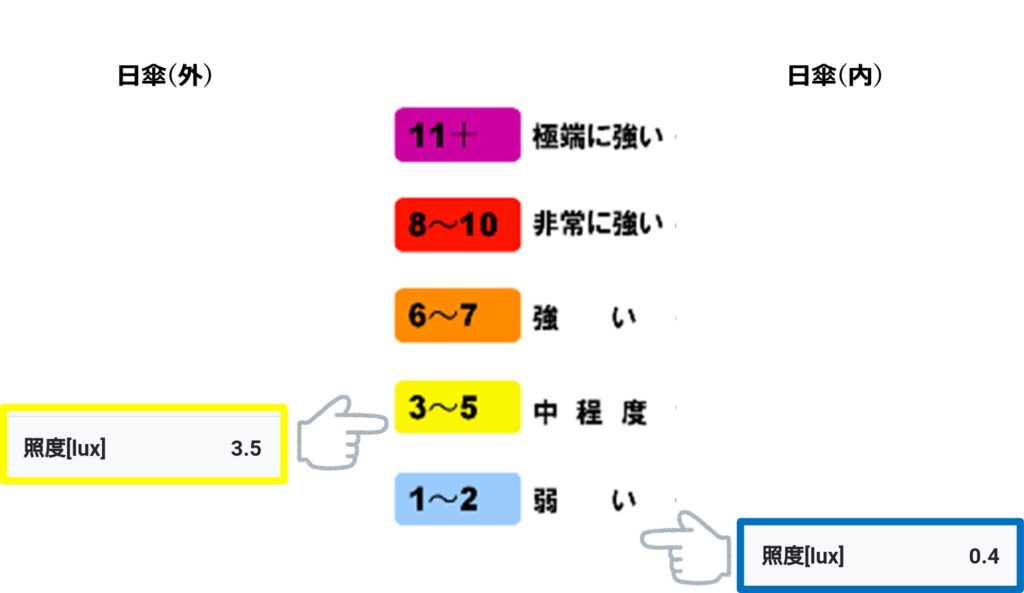

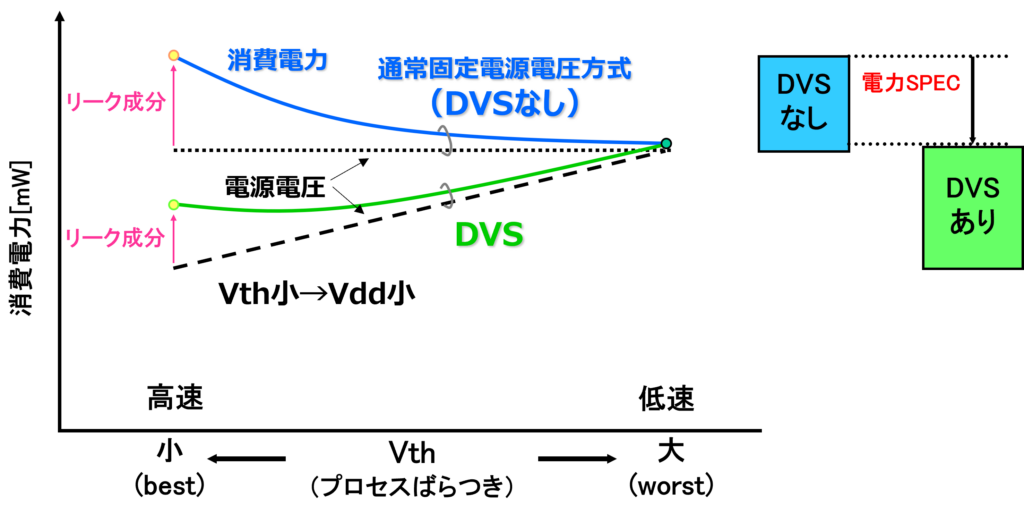

DVSは従来型に比べどの程度省電力化に効果があるのでしょうか?

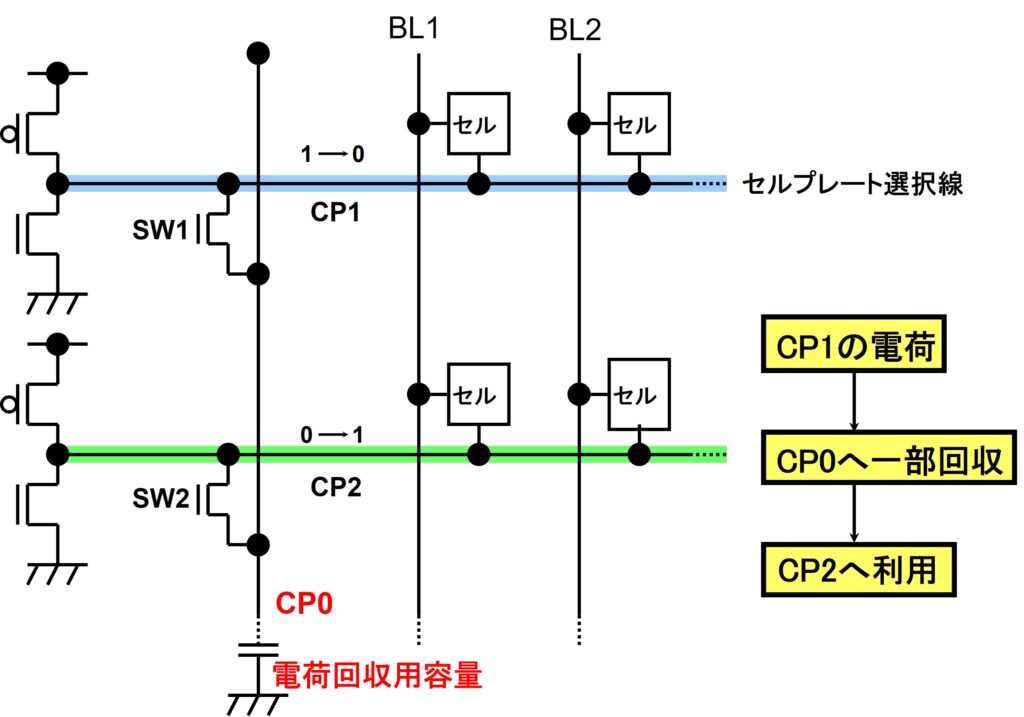

図3にDVSの効果を示します。近年はMOS トランジスタの微細化により、サブスレッシュホールド・リーク電流が無視できなくなります。従来の固定電圧方式では、低Vthサンプルでリーク電流の増大に伴う消費電力増加が大きな問題になります。一方でDVSを採用すると、低Vthであっても回路の高速化を図れるため、電源電圧を低減でき、低消費電力化が図れますので、製品の消費電力SPEC低減に貢献できます。

- MOS動作周波数 Fmax ∝ (Vdd-Vth)・μ/ L2

- 微細化するとリーク電流増大→リークが問題となるVth小サンプルをDVSで補償

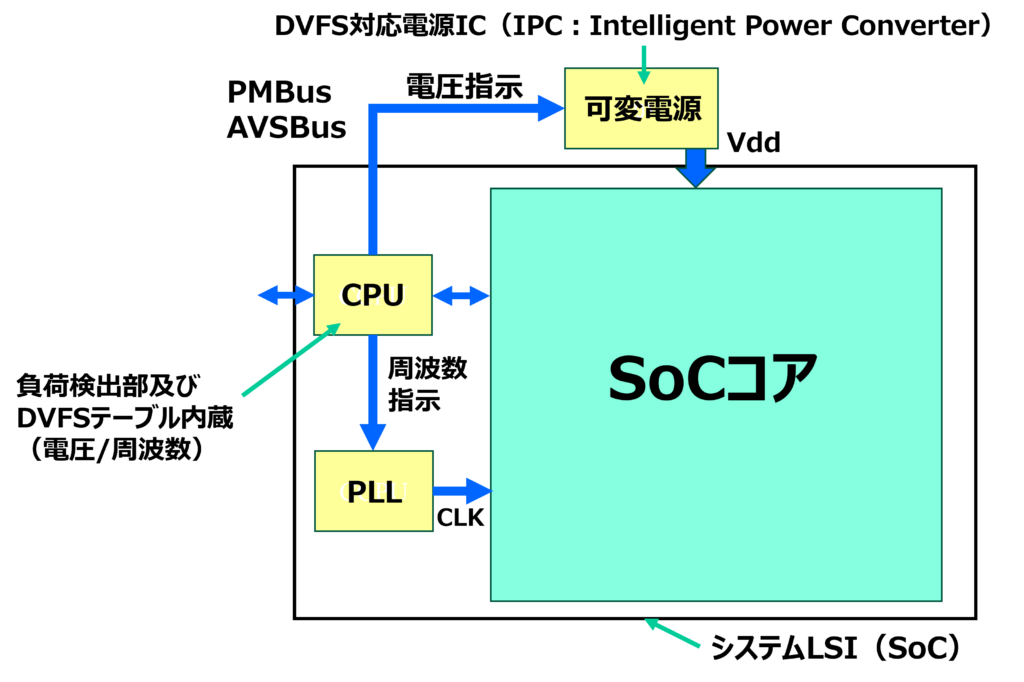

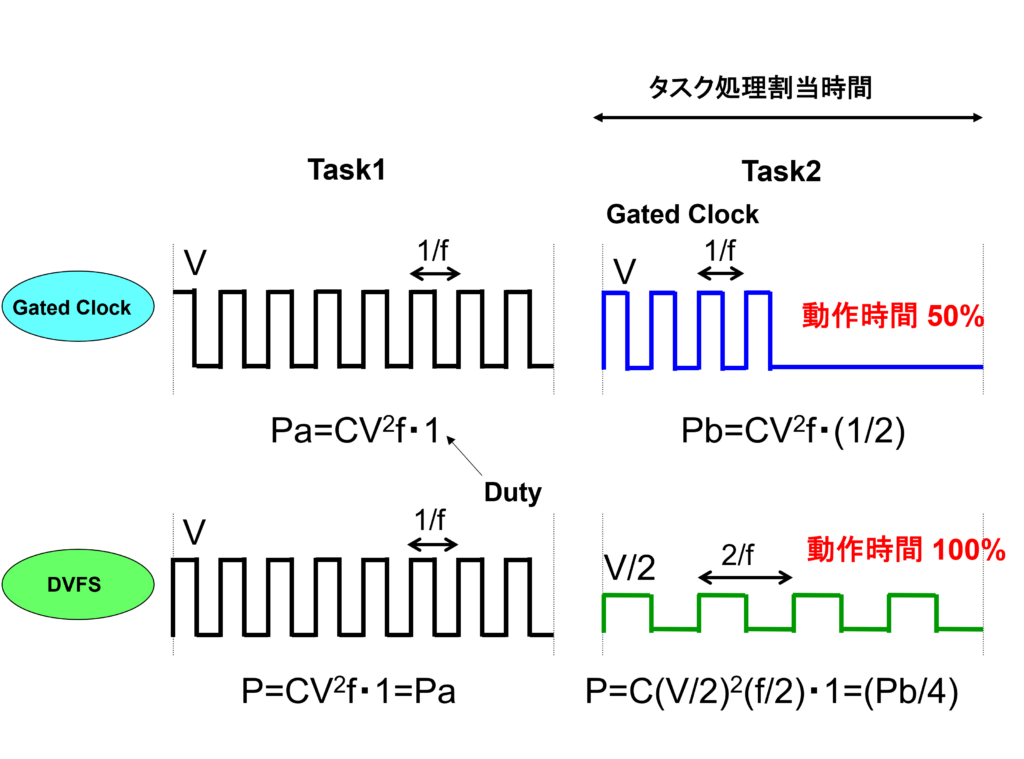

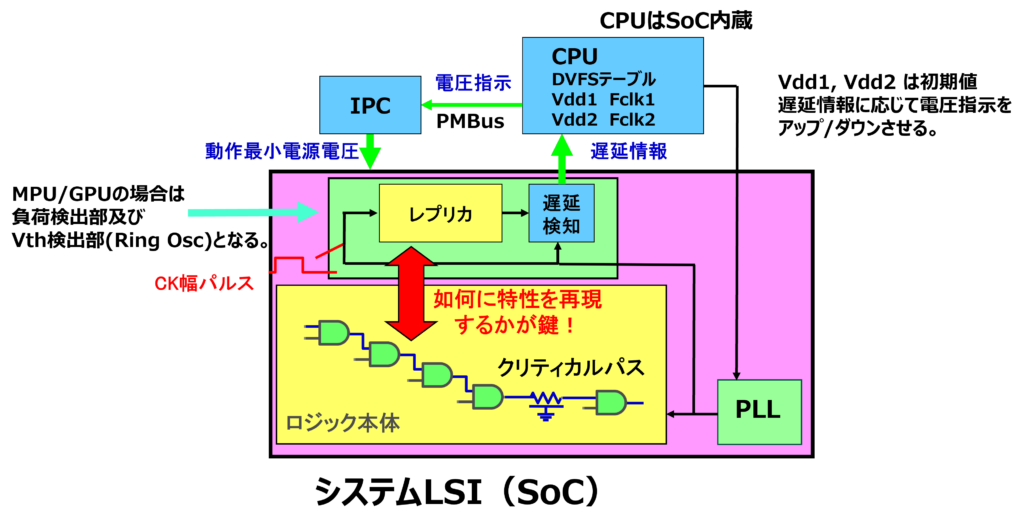

DVFSによる最小電源電圧供給

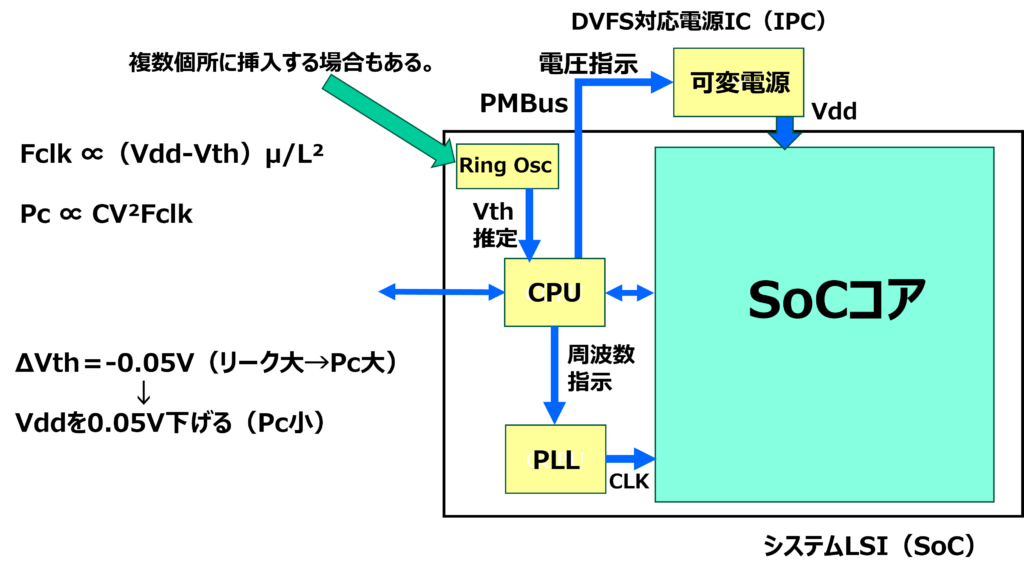

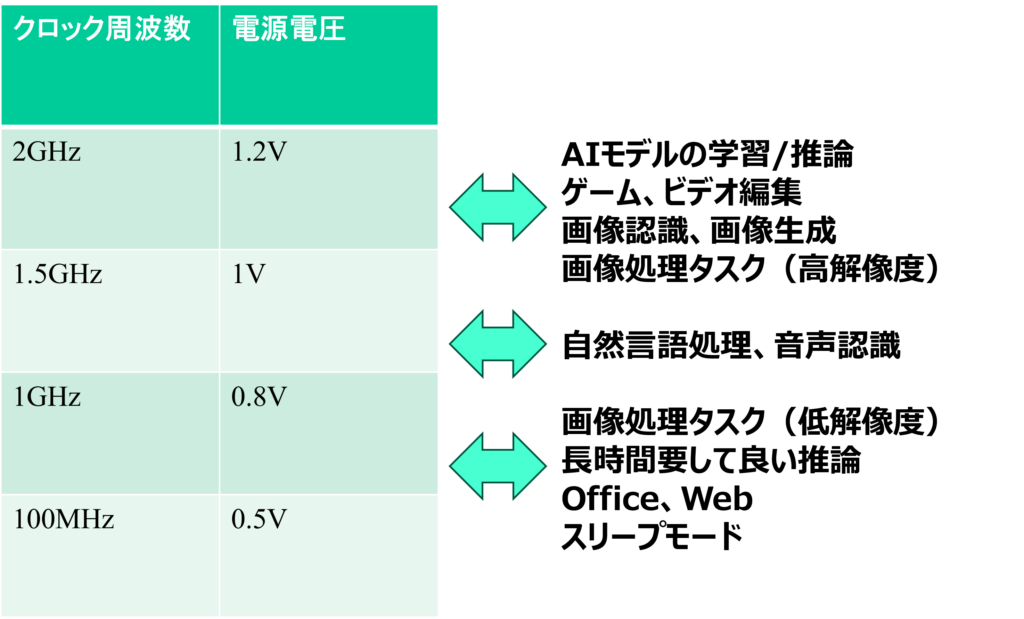

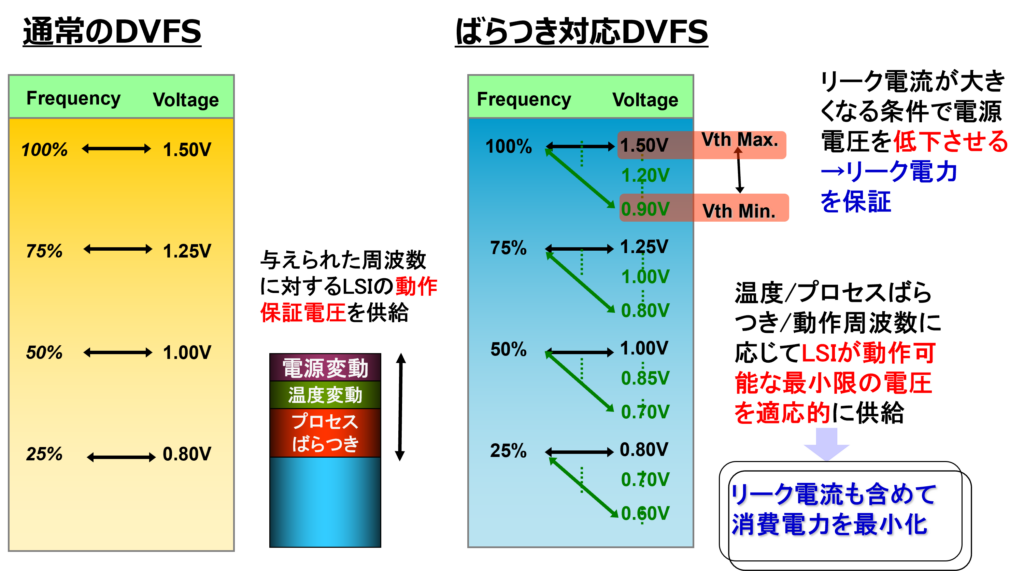

DVSとDVFSの違いは、一言で言うとプロセスばらつき等のworst条件において、電圧だけでなく、動作周波数も考慮に入れて最小電源電圧を供給できる点です。図4にばらつき対応DVFSのブロック図、図5にばらつき対応のDVFSによる最小電源電圧供給を示します。

DVFSは、プロセスばらつき/温度変動/動作周波数に応じて、SoCが動作する最小限の電圧を適用的に供給します。SoC内蔵のCPUがレプリカからの遅延情報を電圧指示に変えるのですが、これがMPU/GPUの場合は負荷検出部及びVt検出部(Ring Osc)からの情報がレプリカに与えられます。

ばらつき対応DVFSであれば、動作周波数に応じリーク電流が大きくなる条件で電源電圧を下げるので、リーク電力が保証されます。すなわち、Worst条件に応じて動的にLSIが動作可能な最低限の電圧を供給します。この結果リーク電流を含めて消費電力を最小化できます。

まとめ

最後にDVFSのまとめを示します。

| 1.プロセッサ系のMPU/GPU/SoCでは素子バラツキ対応を含めたDVFSが幅広く使われている。 |

| 2.DVFSは負荷状態に応じて、動的に電源電圧、クロック周波数を制御する。 |

| 3. 素子バラツキを考慮したDVFSは低消費電力化の効果が大きい。 |

| 4. DVFSは、今後プロセッサのみならず各種SoC(ASIC)にも幅広く使われていく。 |

いかがでしたでしょうか。この記事がLSIの低電力化における皆様のご理解の一助に慣れればうれしいです。